神经形态计算旨在利用硬件和软件算法来模拟生物神经系统的结构和功能单元,从而构建出类似于大脑的具有自主学习能力和认知功能的高能效智能计算系统。为了在硬件上实现神经形态计算,需要寻找低能耗的新型电子器件来模拟神经突触的功能。随着二维材料制备工艺的快速发展,基于二维材料的突触器件研究越来越受到关注。

近日,我院左成杰教授与孙海定研究员组成的联合研究团队在低能耗浮栅型突触器件方面取得进展。该团队制备的新型“二硒化钨-二硫化钼(WSe2-MoS2)浮栅异质结”结构,用于模拟突触行为时,表现出较低的非线性度υp/υd = -2.0/-2.5,单次增强突触型事件能耗更是降低到了阿焦量级(9 × 10-18 J)。相关成果以“High-Performance Floating Gate Heterostructure with WSe2-MoS2 Diode Channel for Neural Synapse”为题于5月23日发表在电子器件领域知名期刊IEEE Electron Device Letters上。

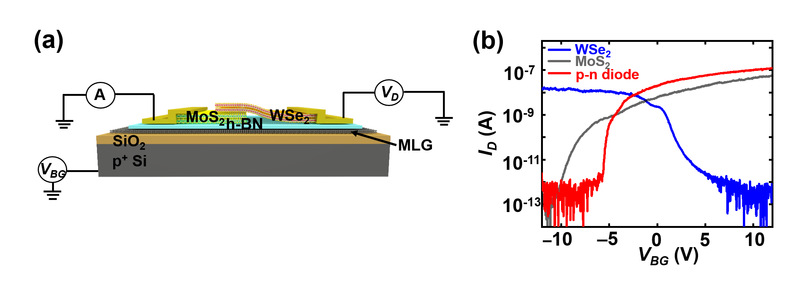

图1. (a)WSe2-MoS2二极管浮栅异质结结构图;(b)WSe2-MoS2二极管、WSe2沟道和MoS2沟道的转移特性曲线。

研究人员提出了一种用WSe2-MoS2二极管作为浮栅异质结沟道的设想,其结构如图1(a)所示。相比于传统的单一二维材料半导体沟道,这种二极管沟道具有更灵敏的栅控特性。这具体表现为,二极管沟道结构比单一二维材料沟道有着更低的亚阈值摆幅,如图1(b)所示。对应WSe2-MoS2二极管、WSe2和MoS2三种不同沟道结构的测试所得的亚阈值摆幅分别为0.21、1.86和0.96 V/dec。

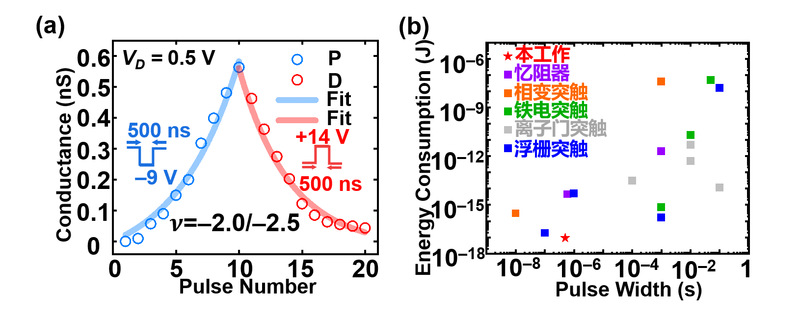

图2. (a)十个增强型前突触刺激和十个抑制型前突触刺激;(b)不同类型突触器件单个突触事件的能耗对比。

研究人员将施加在背栅的电脉冲信号作为前突触刺激,沟道电流作为后突触电流,从而模拟神经突触的可塑性。如图2(a)所示,依次施加十个增强型前突触刺激和十个抑制型前突触刺激,后突触电流随脉冲数发生变化,在增强过程和抑制过程的非线性度分别为υp = -2.0和υd = -2.5。由于突触器件实现的单个突触事件能耗随电刺激脉冲持续时间的减少而减小,在500 ns的电刺激脉冲下所得到的器件能耗为9 aJ,这远低于生物体神经系统单个突触事件的能耗(约为10 fJ)。如图2(b)所示,与其它类型的突触器件比较,该器件实现了文献中最低的工作能耗,为低能耗神经形态(类脑)计算提供了可能。

中国科学技术大学微电子学院左成杰教授、孙海定研究员为论文的通讯作者,微电子学院博士生苏子佳为论文第一作者。此项研究工作得到了国家重点研发计划和国家自然科学基金的资助,也得到了中国科大微电子学院、信息科学技术学院、微纳研究与制造中心、先进技术研究院以及中国科学院无线光电通信重点实验室的支持。

论文链接:

https://doi.org/10.1109/LED.2023.3278454

(中国科学技术大学微电子学院)